- Published on

I2C explained

- Authors

- Name

- JaeHyeok CHOI

- none

I2C 인터페이스

두 개의 I2C 버스 각각은 4.7K 저항을 3.3V로 풀업하여 사용하며 버스에 출력이 없을 경우 High로 풀링된다. 24LC04의 쓰기 보호는 활성화 되지 않는다.

I2C 버스 프로토콜 및 타이밍

I2C 표준 속도는 100kbit/s 이고 고속 모드는 400kbit/s 이다. 다중 시스템 통신과 다중 마스터 제어 모듈을 지원하지만 동시에 하나의 마스터만 허용된다. 직렬 버스는 데이터 라인 SDA와 클록 SCL로 구성되며 각 회로와 모듈은 고유한 주소를 갖는다.

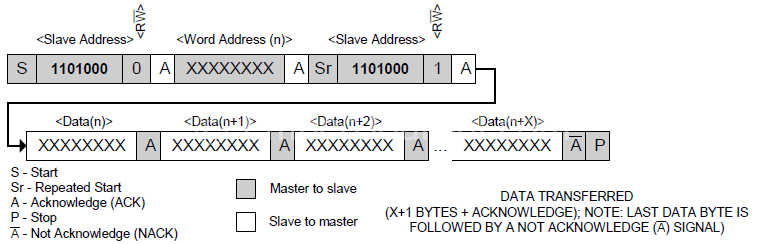

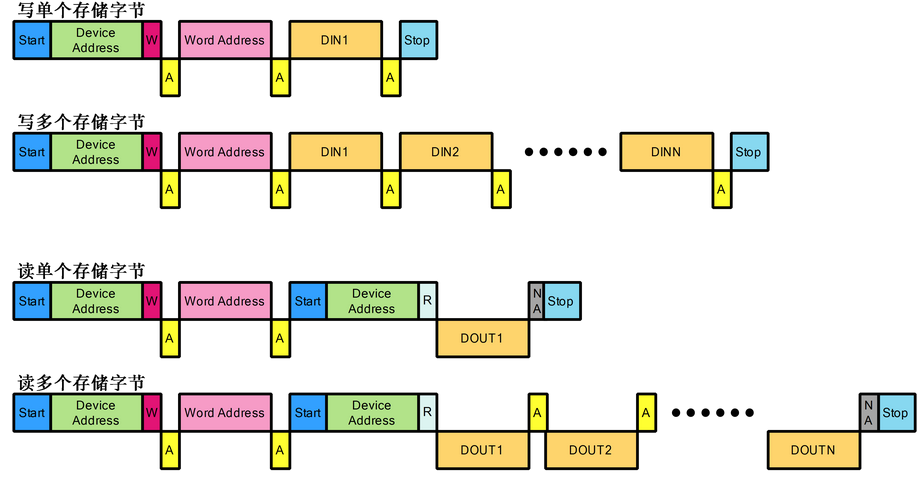

여기서는 I2C 읽기 및 쓰기의 기본 작업과 타이밍을 설명하기 위해 AT24C04를 예로 든다. I2C 장치의 작업은 단일 저장소 바이트 쓰기, 다중 저장소 바이트 쓰기, 단일 저장소 바이트 읽기 및 다중 저장소 바이트 읽기로 나눌 수 있다.

버스 유휴 상태

I2C 버스의 두 신호 라인 SDA와 SCL이 동시에 하이 레벨이 있을 때 이를 버스의 IDLE 상태로 정의한다. 이 때, 각 소자의 출력단 전계효과 트랜지스터는 차단 상태, 즉 버스가 해제되고 두 신호선의 각각의 풀업 저항에 의해 레벨이 하이로 풀링된다.

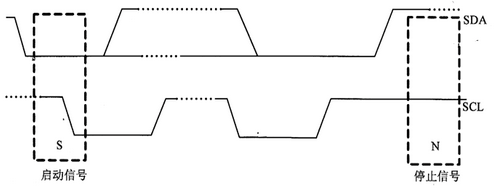

시작 신호

클록 라인 SCL이 하이로 유지되는 동안 데이터 라인 SDA의 레벨은 로우로 풀링된다. (UART Start bit 과 유사) 이는 데이터 전송의 시작을 표시하는 I2C 버스의 시작 신호로 정의된다. 시작 신호는 아래 그림과 같이 이 신호를 설정하기 전에 마스터 컨트롤러에 의해 능동적으로 설정된다.

정지 신호

클록 라인 SCL이 하이 상태를 유지하는 동안 데이터 라인 SDA가 해제되어 하이 레벨 (positive)로 되돌아가게 되면 이를 i2c 버스의 정지 신호라고 하며 데이터의 종료를 표시한다. 정지 신호도 마스터 컨트롤러에 의해 설정되며 신호가 설정된 후 I2C 버스는 IDLE 상태로 돌아간다.

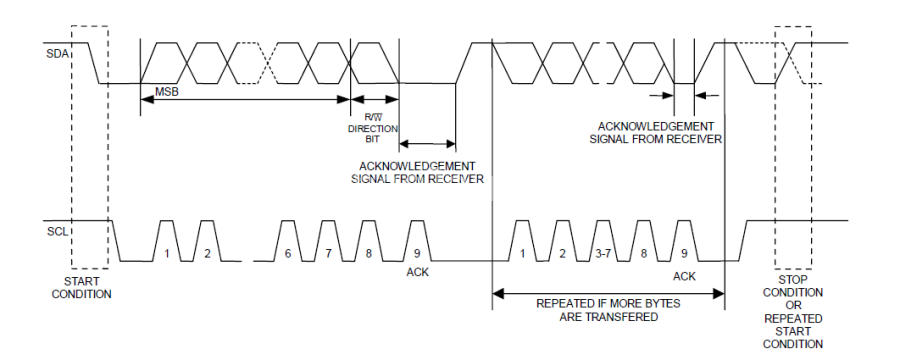

데이터 비트 전송

I2C 버스에서 전송되는 데이터 비트는 클록 펄스 (또는 동기식으로 제어됨)에 해당한다. 즉, SCL 직렬 클록의 협력을 통해 각 데이터 비트는 SDA에서 비트별로 직렬로 전송된다. 데이터를 전송할 때 SCL이 High인 기간 동안 SDA의 레벨은 안정적으로 유지되어야 한다. 로우 레벨은 데이터 0이고 하이 레벨은 데이터 1이다. SDA의 레벨은 SCL이 낮은 동안에만 상태를 변경할 수 있다.

응답 신호 (ACK, NACK)

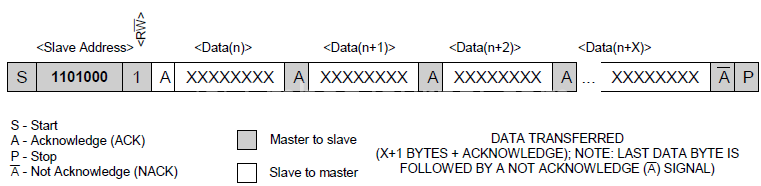

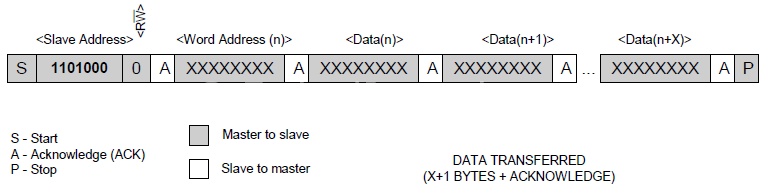

I2C 버스의 모든 데이터는 8비트 바이트로 전송된다. 송신기가 바이트를 보낼 때마다 클럭 펄스 동안 데이터 라인을 해제하고 수신기는 응답 신호를 피드백한다. 응답 신호가 로우 레벨인 경우 유효한 응답 비트 (ACK)로 지정되어 수신기가 바이트를 성공적으로 수신했음을 나타낸다.

응답신호가 하이 레벨인 경우 NACK (비확인 비트)로 지정되며, 이는 수신기가 바이트를 제대로 수신하지 못했음을 나타내며, 유효한 비트 ACK의 피드백에 대한 요구사항은 수신기가 9번째 클록 펄스 이전의 로우 레벨 동안 SDA 라인을 로우로 풀링하고 이 클록의 하이 레벨 동안 안정적인 로우 레벨을 보장한다는 것이다.

수신기가 마스터인 경우 마지막 바이트를 수신한 후 NACK 신호를 보내 제어 대상 송신기에 데이터 전송을 종료하도록 알리고 마스터 수신기가 중지 신호를 보낼 수 있도록 SDA 라인을 해제한다.

Embedded Journal 참고 자료

타이밍 다이어 그램

I2C Read

I2C Write

I2C Read & Write